Intel Rst Windows 7

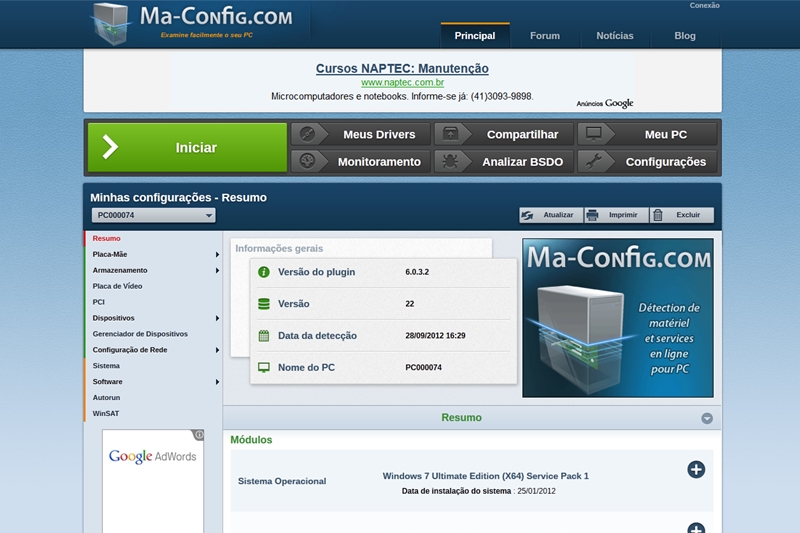

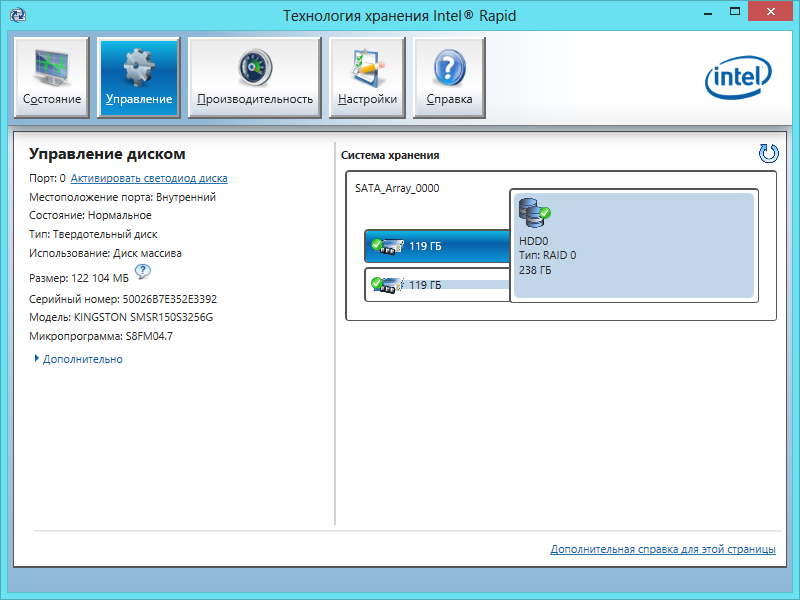

A Modsigned Intel RSTe drivers v15. Intel RST drivers from the v15. Get the resources, documentation and tools you need for the design, development and engineering of Intel based hardware solutions. Windows 7 Intel X38 Driver question. Help Intel Management Engine 5M vs. M Memory Management bsod Intel Management Engine Interface Intel i3 vs core 2 duo. Download Intel Driver Update Utility 3. OS support Windows all. Category System Updates. Support product highlights, featured content, downloads and more for Intel Rapid Storage Technology Intel RST. I have an icon in the lower right tray that says Intel RST Service is not running. What does this mean, do I need to fix it and how do I fix it Ethernet Drivers Intel 945GM Graphics Driver Intel Chipsets Driver Intel Graphics Media Accelerator Driver Ver. Intel PRO Network Adapter Driver. PCIe 3. 0 x16 slots 2 x PLX PEX 8747 bridges, Support 4Way SLICrossFireX in full x16 PCIe 3. SAS2SATA3 from LSI SAS 2308 PCIe 3. Controller. I just installed a new Kingston 300V 120GB SSD. Windows 7 Home Premium SP1 on a Lenovo CIH61M v1. MB from 2011ish sees it and I can copy files tofrom it. But the.  Intel 8. Wikipedia. The Intel 8. Intel and introduced in 1. It is a software binary compatible with the more famous Intel 8. However, it requires less support circuitry, allowing simpler and less expensive microcomputer systems to be built. The 5 in the part number highlighted the fact that the 8. V power supply by using depletion mode transistors, rather than requiring the 5 V, 5 V and 1. Download The Game Of Life 1998 Free'>Download The Game Of Life 1998 Free. V supplies needed by the 8. This capability matched that of the competing Z8. O4xto0c71xI/Umm9xOwt0hI/AAAAAAAAABI/QnfkAdyYlHM/w1200-h630-p-k-no-nu/notebook-positivo-sim-2560m-drivers.jpg' alt='Intel Rst Windows 7' title='Intel Rst Windows 7' />Should I remove IntelR Rapid Storage Technology by Intel Intel174 Rapid Storage Technology offers new levels of protection, performance and expandability for. Intel Rst Windows 7' title='Intel Rst Windows 7' />

Intel 8. Wikipedia. The Intel 8. Intel and introduced in 1. It is a software binary compatible with the more famous Intel 8. However, it requires less support circuitry, allowing simpler and less expensive microcomputer systems to be built. The 5 in the part number highlighted the fact that the 8. V power supply by using depletion mode transistors, rather than requiring the 5 V, 5 V and 1. Download The Game Of Life 1998 Free'>Download The Game Of Life 1998 Free. V supplies needed by the 8. This capability matched that of the competing Z8. O4xto0c71xI/Umm9xOwt0hI/AAAAAAAAABI/QnfkAdyYlHM/w1200-h630-p-k-no-nu/notebook-positivo-sim-2560m-drivers.jpg' alt='Intel Rst Windows 7' title='Intel Rst Windows 7' />Should I remove IntelR Rapid Storage Technology by Intel Intel174 Rapid Storage Technology offers new levels of protection, performance and expandability for. Intel Rst Windows 7' title='Intel Rst Windows 7' />

CPU introduced the year before. These processors could be used in computers running the CPM operating system. The 8. 08. 5 is supplied in a 4. DIP package. To maximise the functions on the available pins, the 8. However, an 8. 08. Intel manufactured several support chips with an address latch built in. These include the 8. KB of EPROM and 1. IO pins, and the 8. RAM, 2. 2 IO pins and a 1. The multiplexed addressdata bus reduced the number of PCB tracks between the 8. IO chips. Both the 8. Zilog Z8. 0 for desktop computers, which took over most of the CPM computer market, as well as a share of the booming home computer market in the early to mid 1. The 8. 08. 5 had a long life as a controller, no doubt thanks to its built in serial IO and 5 prioritized interrupts, arguably microcontroller like features that the Z8. CPU did not have. Alexandra Burke Renegade. Once designed into such products as the DECtape II controller and the VT1. This was typically longer than the product life of desktop computers. DescriptioneditThe 8. Neumann design based on the Intel 8. Unlike the 8. 08. State signals are provided by dedicated bus control signal pins and two dedicated bus state ID pins named S0 and S1. Pin 4. 0 is used for the power supply 5 V and pin 2. Pin 3. 9 is used as the Hold pin. The processor was designed using n. MOS circuitry, and the later H versions were implemented in Intels enhanced n. MOS process called HMOS High performance MOS, originally developed for fast static RAM products. Only a single 5 volt power supply is needed, like competing processors and unlike the 8. The 8. 08. 5 uses approximately 6,5. The 8. 08. 5 incorporates the functions of the 8. A downside compared to similar contemporary designs such as the Z8. Intel 8. 15. 5, 8. The 8. 08. 5 has extensions to support new interrupts, with three maskable vectored interrupts RST 7. RST 6. 5 and RST 5. TRAP, and one externally serviced interrupt INTR. Each of these five interrupts has a separate pin on the processor, a feature which permits simple systems to avoid the cost of a separate interrupt controller. The RST 7. 5 interrupt is edge triggered latched, while RST 5. All interrupts are enabled by the EI instruction and disabled by the DI instruction. In addition, the SIM Set Interrupt Mask and RIM Read Interrupt Mask instructions, the only instructions of the 8. RST interrupts to be individually masked. All three are masked after a normal CPU reset. SIM and RIM also allow the global interrupt mask state and the three independent RST interrupt mask states to be read, the pending interrupt states of those same three interrupts to be read, the RST 7. SOD and SID pins, respectively, all under program control and independently of each other. SIM and RIM each execute in 4 clock cycles T states, making it possible to sample SID andor toggle SOD considerably faster than it is possible to toggle or sample a signal via any IO or memory mapped port, e. In this way, SID can be compared to the SO Set Overflow pin of the 6. CPU contemporary to the 8. Like the 8. 08. 0, the 8. READY, and has provisions for Direct Memory Access DMA using HOLD and HLDA signals pins 3. An improvement over the 8. MHz crystal would yield a 3. MHz clock, for instance. The internal clock is available on an output pin, to drive peripheral devices or other CPUs in lock step synchrony with the CPU from which the signal is output. The 8. 08. 5 can also be clocked by an external oscillator making it feasible to use the 8. CPUs, or to synchronize the CPU to an external time reference such as that from a video source or a high precision time reference. The 8. 08. 5 is a binary compatible follow up on the 8. It supports the complete instruction set of the 8. CPU flags except for the ANDANI operation, which sets the AC flag differently. This means that the vast majority of object code any program image in ROM or RAM that runs successfully on the 8. Exceptions include timing critical code and code that is sensitive to the aforementioned difference in the AC flag setting or differences in undocumented CPU behavior. INR, DCR, and the heavily used MOV r,r instruction, are 1 clock cycle faster, but instructions that involve 1. SP register generally 1 cycle slower. It is of course possible that the actual 8. The same is not true of the Z8. As mentioned already, only the SIM and RIM instructions were new to the 8. Programming modeleditIntel 8. Main registers. AFlags. Program Status Word. BCBDEDHLH indirect addressIndex registers. SPStack Pointer. Program counter. PCProgram Counter. Status register SZ AC P CYFlags. The processor has seven 8 bit registers accessible to the programmer, named A, B, C, D, E, H, and L, where A is also known as the accumulator. The other six registers can be used as independent byte registers or as three 1. BC, DE, and HL or B, D, H, as referred to in Intel documents, depending on the particular instruction. Some instructions use HL as a limited 1. As in the 8. 08. 0, the contents of the memory address pointed to by HL can be accessed as pseudo register M. It also has a 1. 6 bit program counter and a 1. Instructions such as PUSH PSW, POP PSW affect the Program Status Word accumulator and flags. The accumulator stores the results of arithmetic and logical operations, and the flags register bits sign, zero, auxiliary carry, parity, and carry flags are set or cleared according to the results of these operations. The sign flag is set if the result has a negative sign i. The auxiliary or half carry flag is set if a carry over from bit 3 to bit 4 occurred. The parity flag is set according to the parity odd or even of the accumulator. The zero flag is set if the result of the operation was 0. Lastly, the carry flag is set if a carry over from bit 7 of the accumulator the MSB occurred. CommandsinstructionseditAs in many other 8 bit processors, all instructions are encoded in a single byte including register numbers, but excluding immediate data, for simplicity. Some of them are followed by one or two bytes of data, which can be an immediate operand, a memory address, or a port number. Coreldraw Graphics Suite X5 Serial Number Crack Idm'>Coreldraw Graphics Suite X5 Serial Number Crack Idm. A NOP no operation instruction exists, but does not modify any of the registers or flags. Like larger processors, it has CALL and RET instructions for multi level procedure calls and returns which can be conditionally executed, like jumps and instructions to save and restore any 1. There are also eight one byte call instructions RST for subroutines located at the fixed addresses 0. These are intended to be supplied by external hardware in order to invoke a corresponding interrupt service routine, but are also often employed as fast system calls. One sophisticated instruction is XTHL, which is used for exchanging the register pair HL with the value stored at the address indicated by the stack pointer. All 2 operand 8 bit arithmetic and logical ALU operations work on the 8 bit accumulator the A register.

CPU introduced the year before. These processors could be used in computers running the CPM operating system. The 8. 08. 5 is supplied in a 4. DIP package. To maximise the functions on the available pins, the 8. However, an 8. 08. Intel manufactured several support chips with an address latch built in. These include the 8. KB of EPROM and 1. IO pins, and the 8. RAM, 2. 2 IO pins and a 1. The multiplexed addressdata bus reduced the number of PCB tracks between the 8. IO chips. Both the 8. Zilog Z8. 0 for desktop computers, which took over most of the CPM computer market, as well as a share of the booming home computer market in the early to mid 1. The 8. 08. 5 had a long life as a controller, no doubt thanks to its built in serial IO and 5 prioritized interrupts, arguably microcontroller like features that the Z8. CPU did not have. Alexandra Burke Renegade. Once designed into such products as the DECtape II controller and the VT1. This was typically longer than the product life of desktop computers. DescriptioneditThe 8. Neumann design based on the Intel 8. Unlike the 8. 08. State signals are provided by dedicated bus control signal pins and two dedicated bus state ID pins named S0 and S1. Pin 4. 0 is used for the power supply 5 V and pin 2. Pin 3. 9 is used as the Hold pin. The processor was designed using n. MOS circuitry, and the later H versions were implemented in Intels enhanced n. MOS process called HMOS High performance MOS, originally developed for fast static RAM products. Only a single 5 volt power supply is needed, like competing processors and unlike the 8. The 8. 08. 5 uses approximately 6,5. The 8. 08. 5 incorporates the functions of the 8. A downside compared to similar contemporary designs such as the Z8. Intel 8. 15. 5, 8. The 8. 08. 5 has extensions to support new interrupts, with three maskable vectored interrupts RST 7. RST 6. 5 and RST 5. TRAP, and one externally serviced interrupt INTR. Each of these five interrupts has a separate pin on the processor, a feature which permits simple systems to avoid the cost of a separate interrupt controller. The RST 7. 5 interrupt is edge triggered latched, while RST 5. All interrupts are enabled by the EI instruction and disabled by the DI instruction. In addition, the SIM Set Interrupt Mask and RIM Read Interrupt Mask instructions, the only instructions of the 8. RST interrupts to be individually masked. All three are masked after a normal CPU reset. SIM and RIM also allow the global interrupt mask state and the three independent RST interrupt mask states to be read, the pending interrupt states of those same three interrupts to be read, the RST 7. SOD and SID pins, respectively, all under program control and independently of each other. SIM and RIM each execute in 4 clock cycles T states, making it possible to sample SID andor toggle SOD considerably faster than it is possible to toggle or sample a signal via any IO or memory mapped port, e. In this way, SID can be compared to the SO Set Overflow pin of the 6. CPU contemporary to the 8. Like the 8. 08. 0, the 8. READY, and has provisions for Direct Memory Access DMA using HOLD and HLDA signals pins 3. An improvement over the 8. MHz crystal would yield a 3. MHz clock, for instance. The internal clock is available on an output pin, to drive peripheral devices or other CPUs in lock step synchrony with the CPU from which the signal is output. The 8. 08. 5 can also be clocked by an external oscillator making it feasible to use the 8. CPUs, or to synchronize the CPU to an external time reference such as that from a video source or a high precision time reference. The 8. 08. 5 is a binary compatible follow up on the 8. It supports the complete instruction set of the 8. CPU flags except for the ANDANI operation, which sets the AC flag differently. This means that the vast majority of object code any program image in ROM or RAM that runs successfully on the 8. Exceptions include timing critical code and code that is sensitive to the aforementioned difference in the AC flag setting or differences in undocumented CPU behavior. INR, DCR, and the heavily used MOV r,r instruction, are 1 clock cycle faster, but instructions that involve 1. SP register generally 1 cycle slower. It is of course possible that the actual 8. The same is not true of the Z8. As mentioned already, only the SIM and RIM instructions were new to the 8. Programming modeleditIntel 8. Main registers. AFlags. Program Status Word. BCBDEDHLH indirect addressIndex registers. SPStack Pointer. Program counter. PCProgram Counter. Status register SZ AC P CYFlags. The processor has seven 8 bit registers accessible to the programmer, named A, B, C, D, E, H, and L, where A is also known as the accumulator. The other six registers can be used as independent byte registers or as three 1. BC, DE, and HL or B, D, H, as referred to in Intel documents, depending on the particular instruction. Some instructions use HL as a limited 1. As in the 8. 08. 0, the contents of the memory address pointed to by HL can be accessed as pseudo register M. It also has a 1. 6 bit program counter and a 1. Instructions such as PUSH PSW, POP PSW affect the Program Status Word accumulator and flags. The accumulator stores the results of arithmetic and logical operations, and the flags register bits sign, zero, auxiliary carry, parity, and carry flags are set or cleared according to the results of these operations. The sign flag is set if the result has a negative sign i. The auxiliary or half carry flag is set if a carry over from bit 3 to bit 4 occurred. The parity flag is set according to the parity odd or even of the accumulator. The zero flag is set if the result of the operation was 0. Lastly, the carry flag is set if a carry over from bit 7 of the accumulator the MSB occurred. CommandsinstructionseditAs in many other 8 bit processors, all instructions are encoded in a single byte including register numbers, but excluding immediate data, for simplicity. Some of them are followed by one or two bytes of data, which can be an immediate operand, a memory address, or a port number. Coreldraw Graphics Suite X5 Serial Number Crack Idm'>Coreldraw Graphics Suite X5 Serial Number Crack Idm. A NOP no operation instruction exists, but does not modify any of the registers or flags. Like larger processors, it has CALL and RET instructions for multi level procedure calls and returns which can be conditionally executed, like jumps and instructions to save and restore any 1. There are also eight one byte call instructions RST for subroutines located at the fixed addresses 0. These are intended to be supplied by external hardware in order to invoke a corresponding interrupt service routine, but are also often employed as fast system calls. One sophisticated instruction is XTHL, which is used for exchanging the register pair HL with the value stored at the address indicated by the stack pointer. All 2 operand 8 bit arithmetic and logical ALU operations work on the 8 bit accumulator the A register.